**Preliminary User's Manual**

NEC

# **USB Host Controller**

$\mu$ PD9210FGC-7EA

Document No. A13286EJ1V0UM00 (1st edition) Date Published July 1998 N CP(N)

© NEC Corporation 1998 Printed in Japan [MEMO]

#### **1** PRECAUTION AGAINST ESD FOR SEMICONDUCTORS

#### Note:

Strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it once, when it has occurred. Environmental control must be adequate. When it is dry, humidifier should be used. It is recommended to avoid using insulators that easily build static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work bench and floor should be grounded. The operator should be grounded using wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with semiconductor devices on it.

#### (2) HANDLING OF UNUSED INPUT PINS FOR CMOS

#### Note:

No connection for CMOS device inputs can be cause of malfunction. If no connection is provided to the input pins, it is possible that an internal input level may be generated due to noise, etc., hence causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using a pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND with a resistor, if it is considered to have a possibility of being an output pin. All handling related to the unused pins must be judged device by device and related specifications governing the devices.

#### **③** STATUS BEFORE INITIALIZATION OF MOS DEVICES

#### Note:

Power-on does not necessarily define initial status of MOS device. Production process of MOS does not define the initial operation status of the device. Immediately after the power source is turned ON, the devices with reset function have not yet been initialized. Hence, power-on does not guarantee out-pin levels, I/O settings or contents of registers. Device is not initialized until the reset signal is received. Reset operation must be executed immediately after power-on for devices having reset function.

PC/AT is a trademark of IBM Corp.

The application circuits and their parameters are for reference only and are not intended for use in actual design-ins.

The export of this product from Japan is regulated by the Japanese government. To export this product may be prohibited without governmental license, the need for which must be judged by the customer. The export or re-export of this product from a country other than Japan may also be prohibited without a license from that country. Please call an NEC sales representative.

#### The information in this document is subject to change without notice.

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in this document.

NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from use of a device described herein or any other liability arising from use of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Corporation or others.

While NEC Corporation has been making continuous effort to enhance the reliability of its semiconductor devices, the possibility of defects cannot be eliminated entirely. To minimize risks of damage or injury to persons or property arising from a defect in an NEC semiconductor device, customers must incorporate sufficient safety measures in its design, such as redundancy, fire-containment, and anti-failure features.

NEC devices are classified into the following three quality grades:

"Standard", "Special", and "Specific". The Specific quality grade applies only to devices developed based on a customer designated "quality assurance program" for a specific application. The recommended applications of a device depend on its quality grade, as indicated below. Customers must check the quality grade of each device before using it in a particular application.

- Standard: Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots

- Special: Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)

- Specific: Aircrafts, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems or medical equipment for life support, etc.

The quality grade of NEC devices is "Standard" unless otherwise specified in NEC's Data Sheets or Data Books. If customers intend to use NEC devices for applications other than those specified for Standard quality grade, they should contact an NEC sales representative in advance.

Anti-radioactive design is not implemented in this product.

# **Regional Information**

Some information contained in this document may vary from country to country. Before using any NEC product in your application, please contact the NEC office in your country to obtain a list of authorized representatives and distributors. They will verify:

- · Device availability

- · Ordering information

- Product release schedule

- · Availability of related technical literature

- Development environment specifications (for example, specifications for third-party tools and components, host computers, power plugs, AC supply voltages, and so forth)

- Network requirements

In addition, trademarks, registered trademarks, export restrictions, and other legal issues may also vary from country to country.

| NEC Electronics Inc. (U.S.)<br>Santa Clara, California<br>Tel: 408-588-6000<br>800-366-9782<br>Fax: 408-588-6130         | <b>NEC Electronics (Germany) GmbH</b><br>Benelux Office<br>Eindhoven, The Netherlands<br>Tel: 040-2445845<br>Fax: 040-2444580 | NEC Electronics Hong Kong Ltd.<br>Hong Kong<br>Tel: 2886-9318<br>Fax: 2886-9022/9044                                                                              |

|--------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 800-729-9288<br><b>NEC Electronics (Germany) GmbH</b><br>Duesseldorf, Germany<br>Tel: 0211-65 03 02                      | NEC Electronics (France) S.A.<br>Velizy-Villacoublay, France<br>Tel: 01-30-67 58 00<br>Fax: 01-30-67 58 99                    | NEC Electronics Hong Kong Ltd.<br>Seoul Branch<br>Seoul, Korea<br>Tel: 02-528-0303<br>Fax: 02-528-4411                                                            |

| Fax: 0211-65 03 490<br><b>NEC Electronics (UK) Ltd.</b><br>Milton Keynes, UK<br>Tel: 01908-691-133<br>Fax: 01908-670-290 | <b>NEC Electronics (France) S.A.</b><br>Spain Office<br>Madrid, Spain<br>Tel: 01-504-2787<br>Fax: 01-504-2860                 | NEC Electronics Singapore Pte. Ltd.<br>United Square, Singapore 1130<br>Tel: 65-253-8311<br>Fax: 65-250-3583                                                      |

| <b>NEC Electronics Italiana s.r.1.</b><br>Milano, Italy<br>Tel: 02-66 75 41<br>Fax: 02-66 75 42 99                       | NEC Electronics (Germany) GmbH<br>Scandinavia Office<br>Taeby, Sweden<br>Tel: 08-63 80 820<br>Fax: 08-63 80 388               | NEC Electronics Taiwan Ltd.<br>Taipei, Taiwan<br>Tel: 02-719-2377<br>Fax: 02-719-5951<br>NEC do Brasil S.A.<br>Cumbica-Guarulhos-SP, Brasil<br>Tel: 011-6465-6810 |

J98. 2

Fax: 011-6465-6829

[MEMO]

#### PREFACE

This manual describes a USB host controller that complies with the **Open Host Controller Interface Specification Release 1.0** and **OpenHCI Legacy Support Interface Specification Release Version 1.01**.

Read this manual thoroughly to help ensure smooth system design. Also, be sure to observe the various notes in this manual (general notes, caution points, and restrictions). Operation faults and a reduction in the quality and performance levels of LSI products may occur if these notes are not observed.

Before starting a design, contact your local NEC sales representative or distributor to make sure you have the most recent documentation.

## CONTENTS

| CHAPTE | R 1 FEATURES                                            | 15 |

|--------|---------------------------------------------------------|----|

| 1.1    | Features                                                | 15 |

| 1.2    | Block Diagram                                           | 17 |

| 1.3    | Pin Configuration                                       | 18 |

| 1.4    | Pin Configuration Diagram                               | 19 |

| 1.5    | Pin Names and Pin Numbers                               | 20 |

| СНАРТЕ | R 2 PIN FUNCTIONS                                       | 21 |

| 2.1    | Pin Table                                               | 21 |

| 2.2    | Description of Pin Functions                            | 23 |

| 2.3    | Handling Unused Pins                                    | 26 |

| СНАРТЕ | R 3 DESCRIPTION OF USB HOST CONTROLLER FUNCTIONS        | 27 |

| 3.1    | Overview of USB                                         | 27 |

| 3.2    | Host Controller's Communication Method                  | 30 |

| 3.3    | Endpoint Descriptor                                     | 33 |

|        | 3.3.1 Endpoint descriptor format                        | 33 |

|        | 3.3.2 Endpoint descriptor field definitions             | 34 |

| 3.4    | Transfer Descriptors                                    | 35 |

|        | 3.4.1 General transfer descriptor format                | 35 |

|        | 3.4.2 General transfer descriptor field definitions     | 36 |

|        | 3.4.3 Isochronous transfer descriptor format            | 37 |

|        | 3.4.4 Isochronous transfer descriptor field definitions | 38 |

| 3.5    | Host Controller Communications Area                     | 39 |

|        | 3.5.1 Host controller communications area format        | 39 |

|        | 3.5.2 Host controller communications area description   | 39 |

| 3.6    | HC Mode Changes                                         | 40 |

| 3.7    | List Service Flow                                       | 41 |

| 3.8    | Legacy Operations                                       | 45 |

| CHAPTE | R 4 POWER MANAGEMENT                                    | 51 |

| 4.1    | Overview of Power Management                            | 51 |

| 4.2    | Bus States and Device States                            | 52 |

| 4.3    | Transition Conditions for Bus States and Device States  | 53 |

| 4.4    | Device State Transition Flow                            | 55 |

| CHAPTE | R 5 REGISTER INFORMATION                                | 59 |

| 5.1    | PCI Configuration Space                                 | 59 |

| 5.2    | Operational Registers                                   | 64 |

|        | 5.2.1 Overview of operational registers                 | 65 |

|        |                                                         |    |

|        | 5.2.2 Overview of legacy support registers                                         | 74 |

|--------|------------------------------------------------------------------------------------|----|

| CHAPTE | R 6 ELECTRICAL CHARACTERISTICS                                                     | 77 |

| 6.1    | Buffer List                                                                        | 77 |

| 6.2    | Absolute Maximum Ratings                                                           | 78 |

| 6.3    | Recommended Operating Conditions                                                   | 78 |

| 6.4    | Pin Capacitance                                                                    | 78 |

| 6.5    | DC Characteristics (V <sub>DD</sub> = 3.0 V to 3.6 V, T <sub>A</sub> = 0 to +70°C) | 79 |

| 6.6    | Power Consumption                                                                  | 83 |

| 6.7    | System Clock Ratings                                                               | 83 |

| 6.8    | AC Characteristics (V <sub>DD</sub> = 3.0 V to 3.6 V, T <sub>A</sub> = 0 to +70°C) | 84 |

| CHAPTE | R 7 TIMING CHARTS                                                                  | 87 |

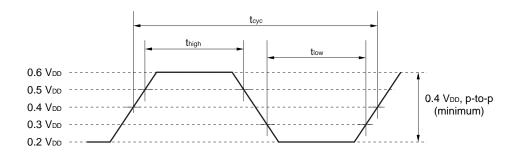

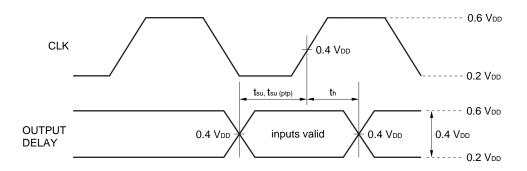

| 7.1    | PCI Clock                                                                          | 87 |

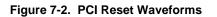

| 7.2    | PCI Reset                                                                          | 87 |

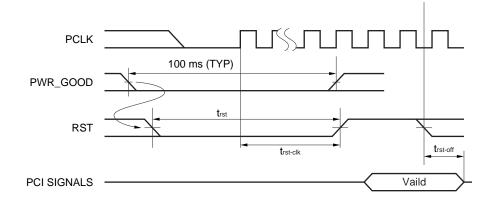

| 7.3    | PCI Output Timing                                                                  | 88 |

| 7.4    | PCI Input Timing                                                                   | 88 |

| 7.5    | PCI Clock Reset                                                                    | 88 |

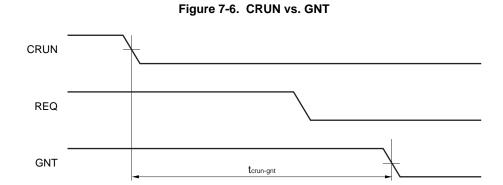

| 7.6    | CRUN vs. GNT                                                                       | 89 |

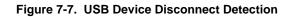

| 7.7    | USB Device Disconnect Detection                                                    | 89 |

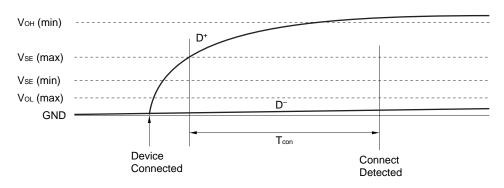

| 7.8    | USB Full Speed Device Connect Detection                                            | 89 |

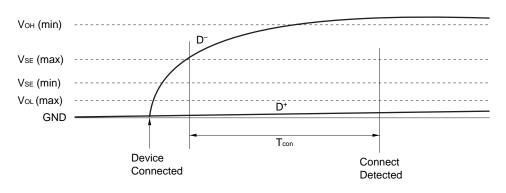

| 7.9    | USB Low Speed Device Connect Detection                                             | 90 |

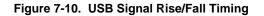

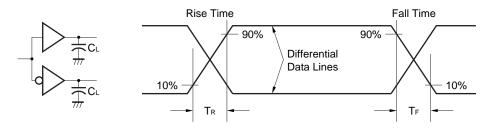

| 7.10   | USB Signal Rise/Fall Timing                                                        | 90 |

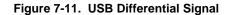

| 7.11   | USB Differential Signal                                                            | 90 |

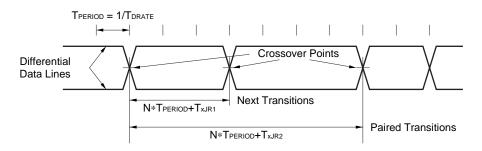

| 7.12   | USB EOP Signal                                                                     | 91 |

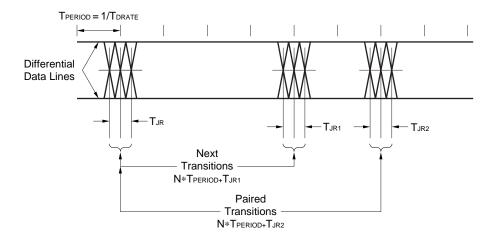

| 7.13   | USB Differential Receiver Allowable Jitter                                         | 91 |

| CHAPTE | R 8 USB HOST CONTROLLER USE METHOD                                                 | 93 |

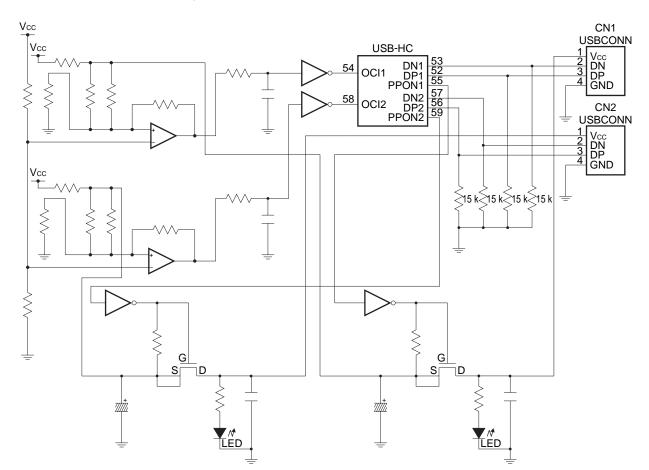

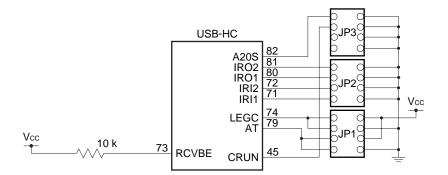

| 8.1    | USB Host Controller Peripheral Circuit Example                                     | 93 |

| Figure | No. Title                                                                     | Page |

|--------|-------------------------------------------------------------------------------|------|

|        |                                                                               |      |

| 1-1    | Block Diagram                                                                 | 17   |

| 1-2    | Pin Configuration                                                             | 18   |

| 1-3    | Pin Configuration Diagram                                                     | 19   |

| 3-1    | Bus Topology                                                                  | 27   |

| 3-2    | Full Speed Device Cable and Resistor Connections                              | 28   |

| 3-3    | Low Speed Device Cable and Resistor Connections                               | 28   |

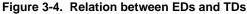

| 3-4    | Relation between EDs and TDs                                                  | 30   |

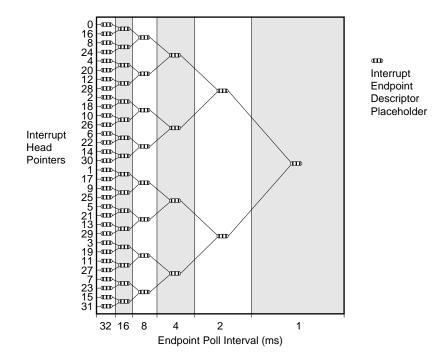

| 3-5    | Interrupt ED List                                                             | 31   |

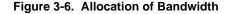

| 3-6    | Allocation of Bandwidth                                                       | 31   |

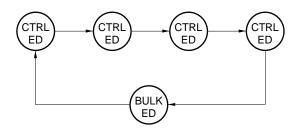

| 3-7    | When Control/Bulk Service Ratio Is 4:1                                        | 32   |

| 3-8    | Endpoint Descriptor Format                                                    | 33   |

| 3-9    | General TD Format                                                             | 35   |

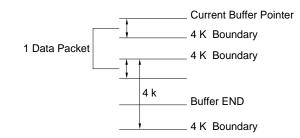

| 3-10   | Current Buffer Pointer/Buffer End and 4-K Boundary                            | 37   |

| 3-11   | Isochronous TD Format                                                         | 37   |

| 3-12   | HC Mode Changes                                                               | 40   |

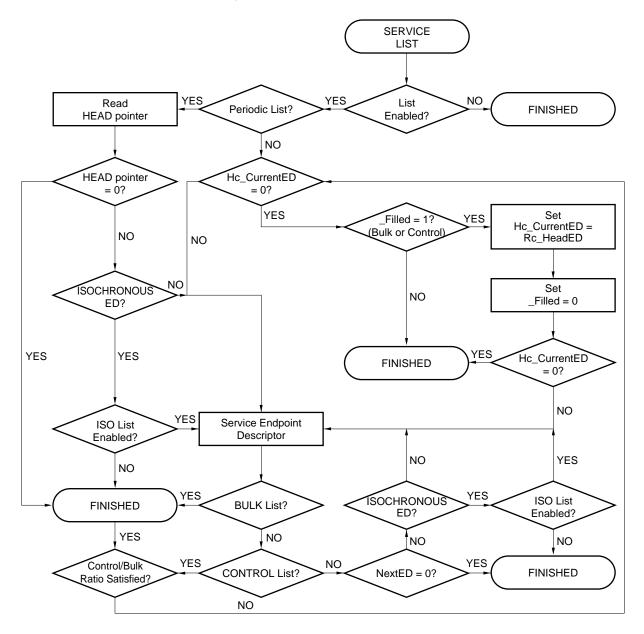

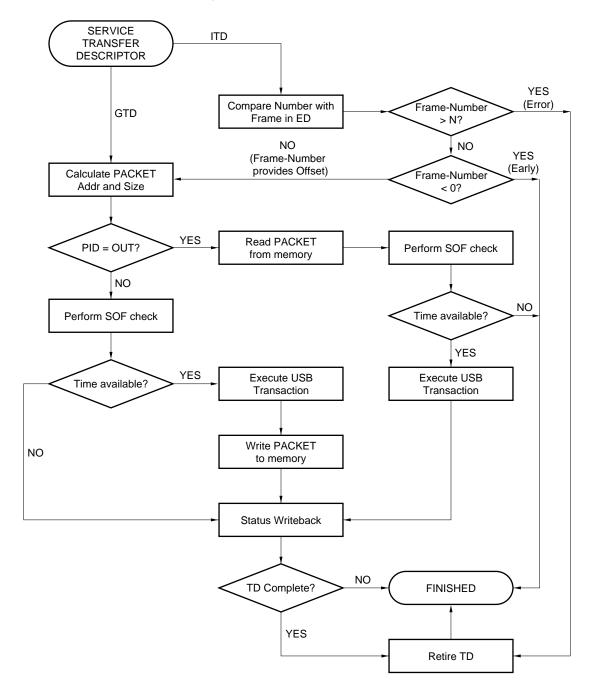

| 3-13   | List Service Flowchart                                                        | 41   |

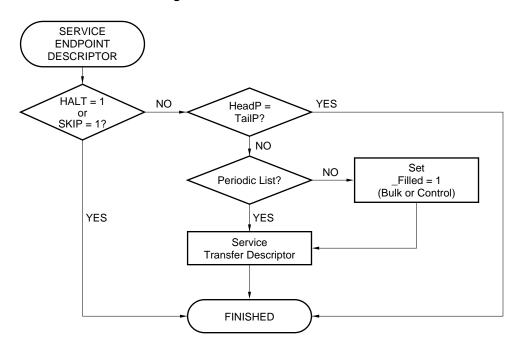

| 3-14   | ED Service Flowchart                                                          | 42   |

| 3-15   | TD Service Flowchart                                                          | 43   |

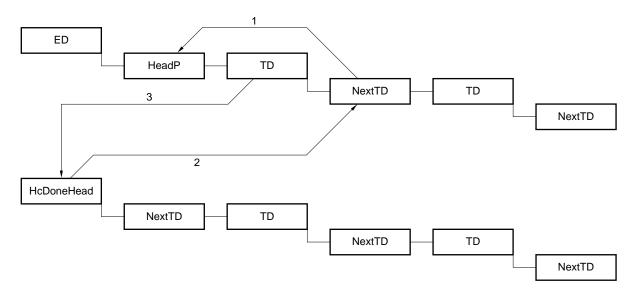

| 3-16   | Done Queue Operations                                                         | 44   |

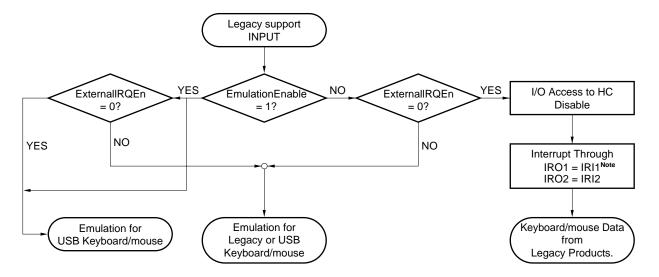

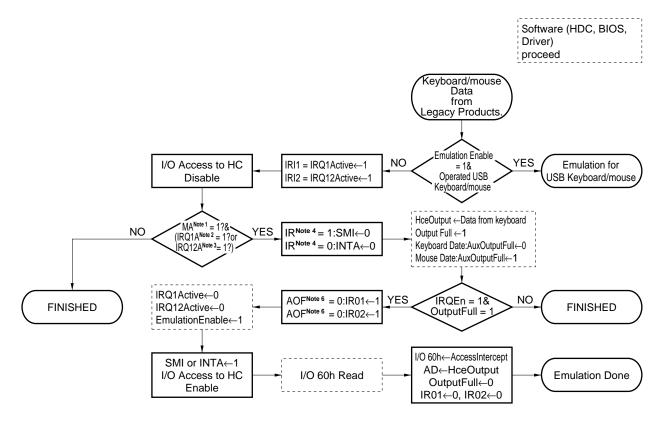

| 3-17   | Input-related Legacy Operation Flowchart                                      | 45   |

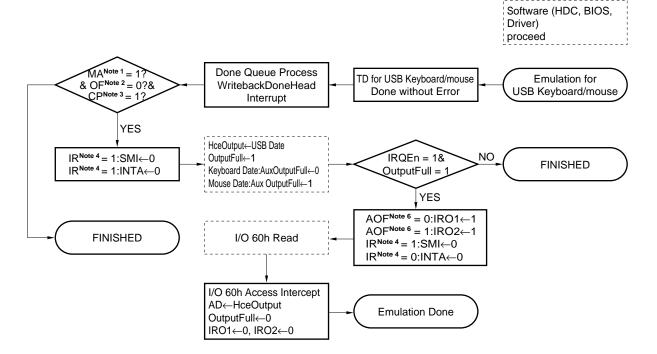

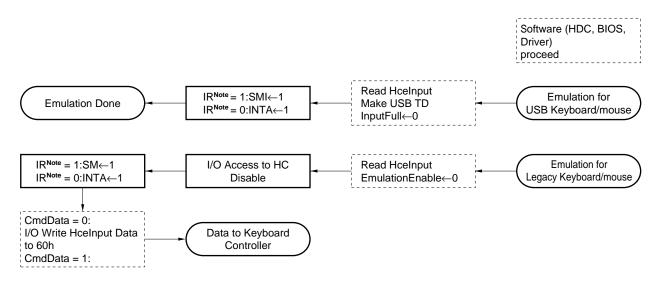

| 3-18   | Input Emulation Flowchart for USB Keyboard/Mouse                              | 46   |

| 3-19   | Combination of USB Keyboard/Mouse and Legacy Keyboard/Mouse (Input Emulation) | 47   |

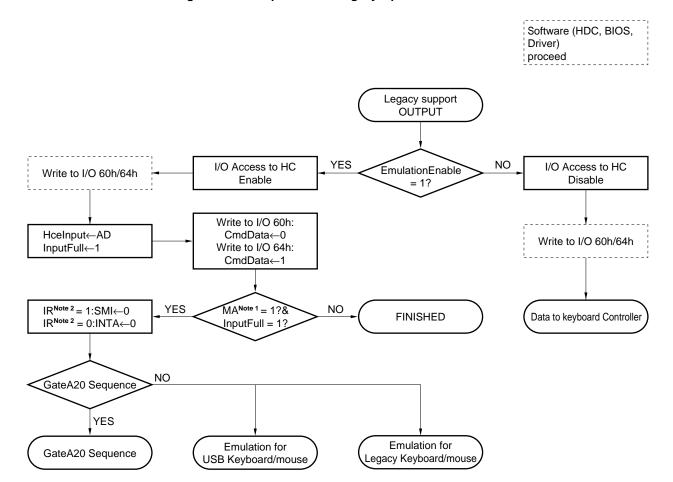

| 3-20   | Output-related Legacy Operation Flowchart                                     | 48   |

| 3-21   | Distinctions between Legacy and USB                                           | 49   |

| 5-1    | OpenHCI's PCI Configuration Space                                             | 63   |

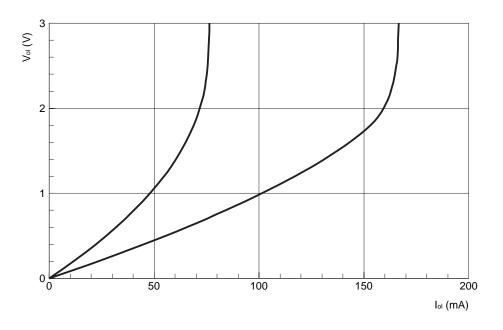

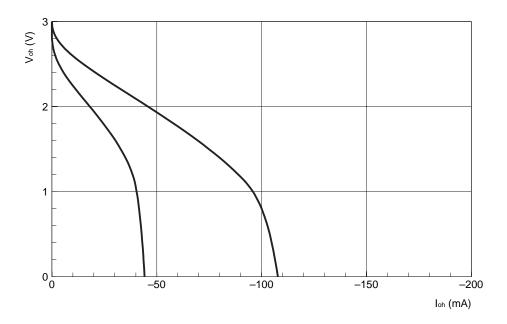

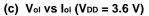

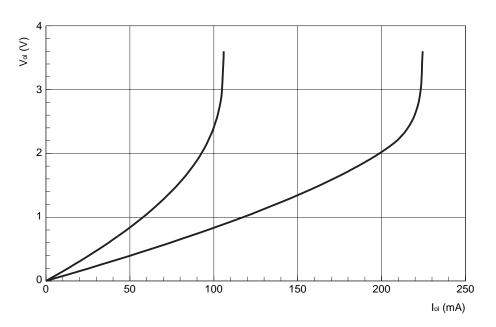

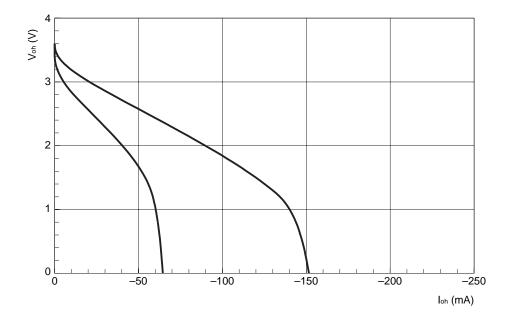

| 6-1    | Vo vs. lo (PCI Buffer)                                                        | 80   |

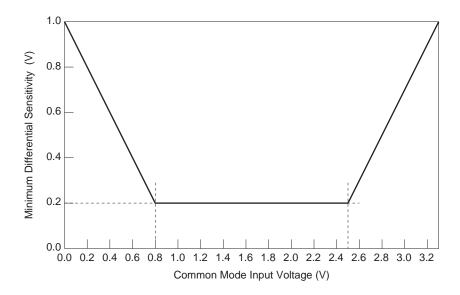

| 6-2    | Vсм (Common Mode Voltage) vs. VDI (Differential Input Sensitivity)            | 82   |

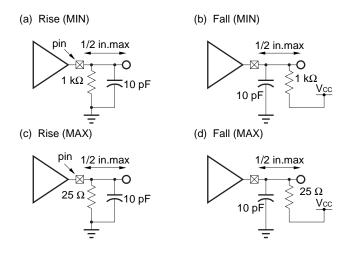

| 7-1    | PCI Clock Waveforms                                                           | 87   |

| 7-2    | PCI Reset Waveforms                                                           | 87   |

| 7-3    | PCI Output Timing                                                             | 88   |

| 7-4    | PCI Input Timing                                                              | 88   |

| 7-5    | PCI Clock Reset                                                               | 88   |

| 7-6    | CRUN vs. GNT                                                                  | 89   |

| 7-7    | USB Device Disconnect Detection                                               | 89   |

| 7-8    | USB Full Speed Device Connect Detection                                       | 89   |

| 7-9    | USB Low Speed Device Connect Detection                                        | 90   |

| 7-10   | USB Signal Rise/Fall Timing                                                   | 90   |

| 7-11   | USB Differential Signal                                                       | 90   |

| 7-12   | USB EOP Signal                                                                | 91   |

| 7-13   | USB Differential Receiver Allowable Jitter Capacitance                        | 91   |

# LIST OF FIGURES (1/2)

| Figure N | No. Title                                 | Page |

|----------|-------------------------------------------|------|

|          |                                           |      |

| 8-1      | Circuit Example of USB Interface Block    | 93   |

| 8-2      | Circuit Example of Legacy Interface Block | 94   |

# LIST OF FIGURES (2/2)

#### LIST OF TABLES

| Table | No. Title                                           | Page |  |

|-------|-----------------------------------------------------|------|--|

| 1-1   | Pin Numbers                                         | 20   |  |

| 2-1   | Pin Table                                           | 21   |  |

| 3-1   | Description of Endpoint Descriptors                 | 34   |  |

| 3-2   | Description of General TD                           | 36   |  |

| 3-3   | Description of Isochronous TD                       | 38   |  |

| 3-4   | Description of Host Controller Communications Area  | 39   |  |

| 3-5   | GateA20 Sequences                                   | 49   |  |

| 4-1   | Device State Transition Conditions                  | 53   |  |

| 4-2   | USB State Transition Conditions                     | 53   |  |

| 4-3   | Mutual Relation between Device State and PCI or USB | 54   |  |

| 4-4   | State Control                                       | 55   |  |

| 5-1   | PCI Configuration Space                             | 59   |  |

| 5-2   | Register Information                                | 60   |  |

| 5-3   | Command Register Information                        | 60   |  |

| 5-4   | Status Register Information                         | 61   |  |

| 5-5   | Base Address (BAR_OHCI) Register Information        | 61   |  |

| 5-6   | I/O Address Register (PC/AT) Information            | 62   |  |

| 5-7   | Power Management Control/Status Information         | 62   |  |

| 5-8   | Host Controller Operational Registers               | 64   |  |

| 5-9   | Legacy Support Registers                            | 64   |  |

| 6-1   | Absolute Maximum Ratings                            | 78   |  |

| 6-2   | Recommended Operating Conditions                    | 78   |  |

| 6-3   | Pin Capacitance                                     | 78   |  |

| 6-4   | DC Characteristics                                  | 79   |  |

| 6-5   | DC Characteristics (PCI Interface Block)            | 79   |  |

| 6-6   | DC Characteristics (USB Interface Block)            | 82   |  |

| 6-7   | DC Characteristics (Control Pin Block)              | 83   |  |

| 6-8   | Power Consumption Characteristics                   | 83   |  |

| 6-9   | System Clock Ratings                                | 83   |  |

| 6-10  | AC Characteristics (PCI Interface Block)            | 84   |  |

| 6-11  | AC Characteristics (USB Interface Block)            | 86   |  |

| 8-1   | Jumper Settings                                     | 94   |  |

[MEMO]

#### **CHAPTER 1 FEATURES**

#### 1.1 Features

#### (1) Functions

- Complies with OpenHCI Specification Release 1.0 and OpenHCI Legacy Support Interface Specification Release Version 1.01.

- Supports asynchronous communication between host CPU and USB devices.

- Supports two types of USB devices: full speed (12 Mbps) devices and low speed (1.5 Mbps) devices.

- System clock: 48 MHz

#### (2) Interface

- USB interface transceiver

- Complies with **Universal Serial Bus Specification Revision 1.0**. Switchable between full speed (12 Mbps) and low speed (1.5 Mbps) modes.

- PCI interface buffer

Complies with PCI Local Bus Specification Revision 2.1 and PCI Mobile Design Guide Revision 1.0.

Supports 32-bit, 33-MHz, 5-VPCI/3.3-VPCI operation.

#### (3) Communication with host CPU

- · Communicates via Operational Registers built into USB host controller

- Communicates via the Host Controller Communication Area in the system memory space

#### (4) Memory and I/O space

- Maps to 4-Kbyte space within the 4-Gbyte system memory space.

- 256-byte Host Controller Communication Area is allocated in the system memory space.

- The legacy support register is allocated to 60h/64h in the I/O space.

#### (5) Legacy support

- USB keyboard + USB mouse, USB keyboard + legacy mouse

- Legacy keyboard + USB mouse, legacy keyboard + legacy mouse

#### (6) On-chip FIFO

- PCI side

- Read: 16 bytes (4  $\times$  4 Dwords), Write: 16 bytes (4  $\times$  4 Dwords)

- USB side

64 bytes (64  $\times$  1 byte)

#### (7) Root Hub

• Equipped with two downstream ports

# (8) Low power consumption

- On-chip clock run function

- On-chip PCI clock stop/USB clock stop functions

#### (9) Others

- CMOS process

- 3-V single power supply

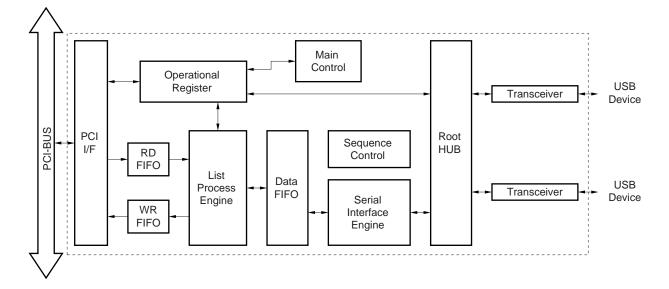

## 1.2 Block Diagram

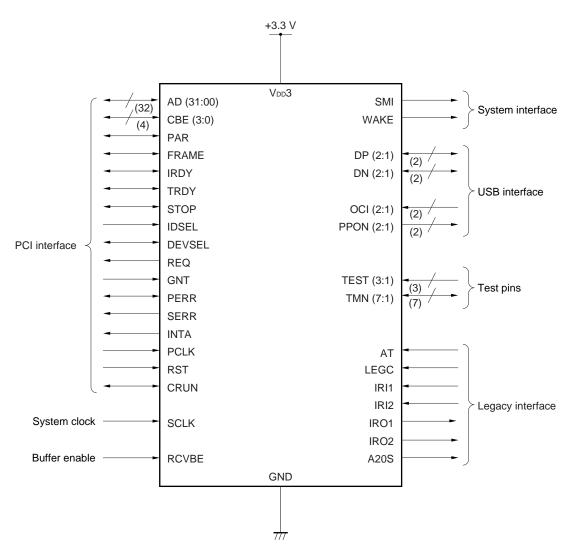

# 1.3 Pin Configuration

Figure 1-2. Pin Configuration

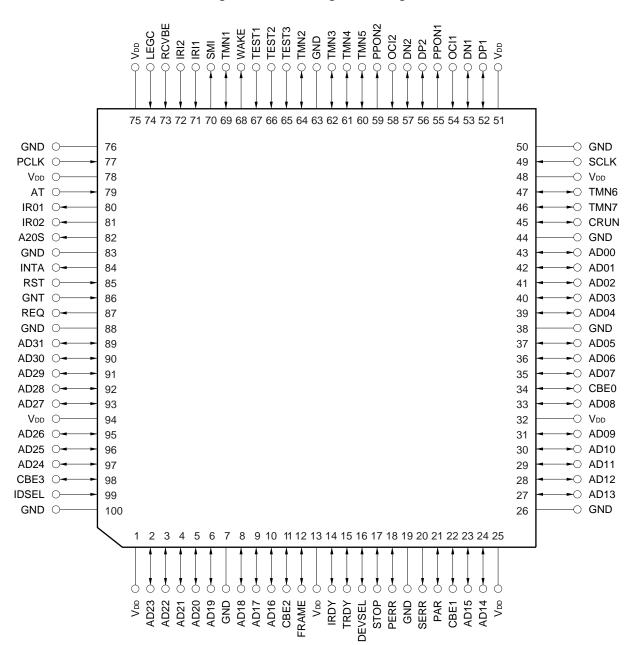

# 1.4 Pin Configuration Diagram

Figure 1-3. Pin Configuration Diagram

#### 1.5 Pin Names and Pin Numbers

| AD (31:00)<br>CBE (3:0) | : PCI Address and Data<br>: PCI Bus Command and Byte Enable | SMI<br>DP (2:1) | : System Management Interrupt<br>: USB D+ |

|-------------------------|-------------------------------------------------------------|-----------------|-------------------------------------------|

| PAR                     | : PCI Parity                                                | DN (2:1)        | : USB D-                                  |

| FRAME                   | : PCI Cycle Frame                                           | OCI (2:1)       | : Over Current Interrupt                  |

| IRDY                    | : PCI Initiator Ready                                       | PPON (2:1)      | : Port Power ON                           |

| TRDY                    | : PCI Target Ready                                          | SCLK            | : System Clock                            |

| STOP                    | : PCI Stop                                                  | RCVBE           | : USB Receiver and Input Buffer Enable    |

| IDSEL                   | : PCI Initialization Device Select                          | AT              | : AT Mode Enable                          |

| DEVSEL                  | : PCI Device Select                                         | LEGC            | : Legacy Support Enable                   |

| REQ                     | : PCI Request                                               | IRI1            | : IRQ1 Input                              |

| GNT                     | : PCI Grant                                                 | IRI2            | : IRQ12 Input                             |

| PERR                    | : PCI Parity Error                                          | IRO1            | : IRQ1 Output                             |

| SERR                    | : PCI System Error                                          | IRO2            | : IRQ12 Output                            |

| INTA                    | : PCI Interrupt                                             | A20S            | : GateA20 State                           |

| PCLK                    | : PCI Clock                                                 | WAKE            | : Wakeup Interrupt                        |

| RST                     | : PCI Reset                                                 | TEST (3:1)      | : TEST Control                            |

| CRUN                    | : PCI Clock running                                         | TMN (7:1)       | : TEST signal                             |

|                         |                                                             |                 |                                           |

#### Table 1-1. Pin Numbers

| Pin Number | Pin Name |

|------------|----------|------------|----------|------------|----------|------------|----------|

| 1          | Vdd      | 26         | GND      | 51         | Vdd      | 76         | GND      |

| 2          | AD23     | 27         | AD13     | 52         | DP1      | 77         | PCLK     |

| 3          | AD22     | 28         | AD12     | 53         | DN1      | 78         | Vdd      |

| 4          | AD21     | 29         | AD11     | 54         | OCI1     | 79         | AT       |

| 5          | AD20     | 30         | AD10     | 55         | PPON1    | 80         | IRO1     |

| 6          | AD19     | 31         | AD09     | 56         | DP2      | 81         | IRO2     |

| 7          | GND      | 32         | Vdd      | 57         | DN2      | 82         | A20S     |

| 8          | AD18     | 33         | AD08     | 58         | OCI2     | 83         | GND      |

| 9          | AD17     | 34         | CBE0     | 59         | PPON2    | 84         | INTA     |

| 10         | AD16     | 35         | AD07     | 60         | TMN5     | 85         | RST      |

| 11         | CBE2     | 36         | AD06     | 61         | TMN4     | 86         | GNT      |

| 12         | FRAME    | 37         | AD05     | 62         | TMN3     | 87         | REQ      |

| 13         | Vdd      | 38         | GND      | 63         | GND      | 88         | GND      |

| 14         | IRDY     | 39         | AD04     | 64         | TMN2     | 89         | AD31     |

| 15         | TRDY     | 40         | AD03     | 65         | TEST3    | 90         | AD30     |

| 16         | DEVSEL   | 41         | AD02     | 66         | TEST2    | 91         | AD29     |

| 17         | STOP     | 42         | AD01     | 67         | TEST1    | 92         | AD28     |

| 18         | PERR     | 43         | AD00     | 68         | WAKE     | 93         | AD27     |

| 19         | GND      | 44         | GND      | 69         | TMN1     | 94         | Vdd      |

| 20         | SERR     | 45         | CRUN     | 70         | SMI      | 95         | AD26     |

| 21         | PAR      | 46         | TMN7     | 71         | IRI1     | 96         | AD25     |

| 22         | CBE1     | 47         | TMN6     | 72         | IRI2     | 97         | AD24     |

| 23         | AD15     | 48         | Vdd      | 73         | RCVBE    | 98         | CBE3     |

| 24         | AD14     | 49         | SCLK     | 74         | LEGC     | 99         | IDSEL    |

| 25         | Vdd      | 50         | GND      | 75         | Vdd      | 100        | GND      |

#### 2.1 Pin Table

#### Table 2-1. Pin Table

| Pin Name     | I/O     | Buffer Type                                                     | Active Level | Function                                           |

|--------------|---------|-----------------------------------------------------------------|--------------|----------------------------------------------------|

| AD (31 : 0)  | I/O     | 5 V PCI I/O                                                     |              | PCI "AD [31 : 0]" signal                           |

| CBE (3:0)    | I/O     | 5 V PCI I/O                                                     |              | PCI "C/BE [3 : 0]" signal                          |

| PAR          | I/O     | 5 V PCI I/O                                                     |              | PCI "PAR" signal                                   |

| FRAME        | I/O     | 5 V PCI I/O                                                     |              | PCI "FRAME#" signal                                |

| IRDY         | I/O     | 5 V PCI I/O                                                     |              | PCI "IRDY#" signal                                 |

| TRDY         | I/O     | 5 V PCI I/O                                                     |              | PCI "TRDY#" signal                                 |

| STOP         | I/O     | 5 V PCI I/O                                                     |              | PCI "STOP#" signal                                 |

| IDSEL        | I       | 5 V PCI Input                                                   |              | PCI "IDSEL" signal                                 |

| DEVSEL       | I/O     | 5 V PCI I/O                                                     |              | PCI "DEVSEL#" signal                               |

| REQ          | 0       | 5 V PCI Output                                                  |              | PCI "REQ#" signal                                  |

| GNT          | I       | 5 V PCI Input                                                   |              | PCI "GNT#" signal                                  |

| PERR         | I/O     | 5 V PCI I/O                                                     |              | PCI "PERR#" signal                                 |

| SERR         | 0       | 5 V PCI N-ch Open Drain                                         |              | PCI "SERR#" signal                                 |

| INTA         | 0       | 5 V PCI N-ch Open Drain                                         | Low          | PCI "INTA#" signal                                 |

| PCLK         | I       | 5 V PCI Input                                                   |              | PCI "CLK" signal                                   |

| RST          | I       | 5 V Schmitt Input                                               | Low          | PCI "RST#" signal                                  |

| CRUN         | I/O     | 5 V PCI I/O (N-ch Open Drain)                                   |              | PCI "CLKRUN#" signal                               |

| SCLK         | I       | 5 V Schmitt Input                                               |              | System clock input                                 |

| SMI          | 0       | 5 V IoL = 12 mA N-ch Open Drain Low                             |              | System management interrupt output                 |

| DP (2 : 1)   | I/O     | USB D+I/O                                                       |              | USB's D+ signal                                    |

| DN (2 : 1)   | I/O     | USB D–I/O                                                       |              | USB's D– signal                                    |

| OCI (2 : 1)  | I (I/O) | 5 V Input with excessive through<br>current prevention function | High         | USB Root Hub Port's overcurrent status input       |

| PPON (2 : 1) | 0       | 5 V IoL = 6 mA Output                                           | High         | USB Root Hub Port's power supply control<br>output |

| RCVBE        | I       | 5 V Input                                                       | High         | USB Receiver and Input Buffer Enable signal        |

| AT           | I (I/O) | 5 V Schmitt Input                                               | High         | Legacy support switch                              |

| LEGC         | l (I/O) | 5 V Schmitt Input                                               | High         | Legacy support switch                              |

| IRI1         | I (I/O) | 5 V Input with excessive through<br>current prevention function | High         | INT input from keyboard                            |

| IRI2         | I (I/O) | 5 V Input with excessive through<br>current prevention function | High         | INT input from mouse                               |

| IRO1         | 0       | 5 V Io∟ = 6 mA N-ch Open Drain                                  | High         | INT output from keyboard                           |

| IRO2         | O (I/O) | 5 V Io∟ = 6 mA N-ch Open Drain                                  | High         | INT output from mouse                              |

| A20S         | O (I/O) | 5 V Io∟= 6 mA N-ch Open Drain                                   | -            | GateA20 State output                               |

| WAKE         | 0       | 5 V lo∟ = 6 mA Output                                           | High         | Wakeup interrupt output                            |

| TEST (3 : 1) | I       | 3 V Input with 50 k $\Omega$ Pull up R                          | -            | Test pin                                           |

| TMN (7 : 1)  | I/O     | 3 V I/O with 50 kΩ Pull up R                                    |              | Test pin                                           |

- **Remarks 1.** The 5-V buffer in the table indicates a 5-V tolerant buffer. "5-V tolerant" means that the buffer is a 3-V buffer with 5-V maximum voltage.

- 2. "5 V PCI" indicates a PCI buffer that has a 5-V maximum voltage circuit which complies with the 3-V PCI standard. It does not indicate a buffer that fully complies with the 5-V PCI standard. However, this function can be used for evaluating the operation of a device by attaching a 5-V add-in card beforehand.

- **3.** The signals marked as "(I/O)" in the above table operate as I/O signals during testing. However, they do not need to be considered in normal use situations.

#### 2.2 Description of Pin Functions

#### • Power supply

| Pin | Pin No.                                    | Direction | Function          |

|-----|--------------------------------------------|-----------|-------------------|

| Vdd | 1, 13, 25, 32, 48, 51, 75, 78, 94          | -         | +3 V power supply |

| GND | 7, 19, 26, 38, 44, 50, 63, 76, 83, 88, 100 | -         | Ground            |

#### • PCI interface

| Pin          | Pin No.                                                                          | Direction | Function                  |

|--------------|----------------------------------------------------------------------------------|-----------|---------------------------|

| AD (31 : 00) | 2 to 6, 8 to 10, 23, 24, 27 to 31, 33,<br>35 to 37, 39 to 43, 89 to 93, 95 to 97 | I/O       | PCI "AD [31 : 00]" signal |

| CBE (3:0)    | 11, 22, 34, 98                                                                   | I/O       | PCI "C/BE [3 : 0]" signal |

| PAR          | 21                                                                               | I/O       | PCI "PAR" signal          |

| FRAME        | 12                                                                               | I/O       | PCI "FRAME#" signal       |

| IRDY         | 14                                                                               | I/O       | PCI "IRDY#" signal        |

| TRDY         | 15                                                                               | I/O       | PCI "TRDY#" signal        |

| STOP         | 17                                                                               | I/O       | PCI "STOP#" signal        |

| IDSEL        | 99                                                                               | I         | PCI "IDSEL" signal        |

| DEVSEL       | 16                                                                               | I/O       | PCI "DEVSEL#" signal      |

| REQ          | 87                                                                               | 0         | PCI "REQ#" signal         |

| GNT          | 86                                                                               | I         | PCI "GNT#" signal         |

| PERR         | 18                                                                               | I/O       | PCI "PERR#" signal        |

| SERR         | 20                                                                               | 0         | PCI "SERR#" signal        |

| INTA         | 84                                                                               | 0         | PCI "INTA#" signal        |

| PCLK         | 77                                                                               | I         | PCI "CLK" signal          |

| RST          | 85                                                                               | I         | PCI "RST#" signal         |

| CRUN         | 45                                                                               | I/O       | PCI "CLKRUN#" signal      |

Remark For details of PCI operations, see the PCI Local Bus Specification Revision 2.1.

# System clock

| Pin  | Pin No. | Direction | Caution                                         |

|------|---------|-----------|-------------------------------------------------|

| SCLK | 49      | I         | System clock input<br>Apply 48-MHz clock input. |

#### • Test pins

| Pin          | Pin No.                    | Direction | Caution                                 |

|--------------|----------------------------|-----------|-----------------------------------------|

| TEST (3 : 1) | 65, 66, 67                 | I         | Be sure to leave open on circuit board. |

| TMN (7 : 1)  | 46, 47, 60, 61, 62, 64, 69 | I/O       | Be sure to leave open on circuit board. |

#### • System interface

| Pin   | Pin No. | Direction | Function                                                                                                                                                                                                                                                                                                                                                                                    |

|-------|---------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SMI   | 70      | 0         | <ul><li>System management interrupt output</li><li>Changed to INTA by ownership change before being output.</li><li>0: Interrupt occurs</li><li>1: Interrupt does not occur</li></ul>                                                                                                                                                                                                       |

| RCVBE | 73      | I         | <ul> <li>USB Receiver/Input Buffer Enable signal</li> <li>0: Excessive through current prevention/differential buffer operating current cut-off function ON</li> <li>1: Excessive through current prevention/differential buffer operating current cut-off function OFF</li> <li>The pins being controlled are as follows.</li> <li>DP (2: 1), DN (2: 1), OCI (2: 1), IRI1, IRI2</li> </ul> |

| WAKE  | 68      | 0         | Wakeup request signal is output from the USB.<br>0: No Wakeup request<br>1: Wakeup request exists                                                                                                                                                                                                                                                                                           |

#### • USB interface

| Pin          | Pin No. | Direction | Function                                                                                                                          |

|--------------|---------|-----------|-----------------------------------------------------------------------------------------------------------------------------------|

| DP (2 : 1)   | 52, 56  | I/O       | USB's D+ signal<br>Shared with DNx pins having the same numbers.                                                                  |

| DN (2 : 1)   | 53, 57  | I/O       | USB's D- signal<br>Shared with DPx pins having the same numbers.                                                                  |

| OCI (2 : 1)  | 54, 58  | I         | Pin for inputting the overcurrent status of the USB Root<br>Hub Port<br>0: No power supply problem<br>1: Overcurrent has occurred |

| PPON (2 : 1) | 55, 59  | 0         | Power supply control output for USB Root Hub Port<br>0: Power supply OFF<br>1: Power supply ON                                    |

| Pin                  | Pin No. | Direction | Function                                                                                                                            |

|----------------------|---------|-----------|-------------------------------------------------------------------------------------------------------------------------------------|

| AT                   | 79      | 1         | Legacy support<br>0: Legacy OFF<br>1: Legacy ON                                                                                     |

| LEGC                 | 74      | I         | Legacy support switch<br>0: Legacy OFF<br>1: Legacy ON<br>When off, "L" clamp IRI1 and IRI2 and leave IRO1,<br>IRO2, and A20S open. |

| IRI1 <sup>Note</sup> | 71      | I         | INT input from keyboard: active H                                                                                                   |

| IRI2 <sup>Note</sup> | 72      | I         | INT input from mouse: active H                                                                                                      |

| IRO1                 | 80      | 0         | INT output from keyboard: active H                                                                                                  |

| IRO2                 | 81      | 0         | INT output from mouse: active H                                                                                                     |

| A20S                 | 82      | 0         | GateA20 State output                                                                                                                |

#### • Legacy support interface

**Note** IRQ is sampled using the 12-MHz clock signal generated by SCLK, and an interrupt is detected as a result. The next IRQ is not received during emulation. After emulation is completed, an interrupt can be received once the IRQ's H level has been sampled.

#### 2.3 Handling Unused Pins

Handle unused pins as shown below.

| Pin          | Direction | Connection Method                                 |

|--------------|-----------|---------------------------------------------------|

| DPx          | I/O       | Connect via 15 k $\Omega$ ±5% pull-down resistor. |

| DNx          | I/O       | Connect via 15 k $\Omega$ ±5% pull-down resistor. |

| OCIx         | I         | "L" clamp                                         |

| PPONx        | 0         | No Connection (Open)                              |

| TEST (3 : 1) | I         | No Connection (Open)                              |

| TMN (1 : 7)  | I/O       | No Connection (Open)                              |

When the legacy function is off (AT = L, LEGC = L), handle unused pins as shown below.

| Pin  | Direction | Connection Method    |

|------|-----------|----------------------|

| IRI1 | I         | "L" clamp            |

| IRI2 | I         | "L" clamp            |

| IRO1 | 0         | No Connection (Open) |

| IRO2 | 0         | No Connection (Open) |

| A20S | 0         | No Connection (Open) |

#### CHAPTER 3 DESCRIPTION OF USB HOST CONTROLLER FUNCTIONS

This chapter provides an overview of the USB, the operations of the host controller, and the structure of the interface data that is used. For details, see the **Open Host Controller Interface Specification Release 1.0** and **OpenHCI Legacy Support Interface Specification Release Version 1.01**.

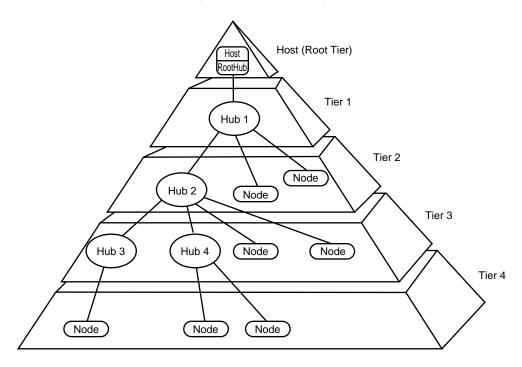

#### 3.1 Overview of USB

The USB (Universal Serial Bus) is a type of serial bus that enables transfer of data between a host computer and various types of peripheral devices. The USB host has point-to-point connections with USB devices via a tiered star topology, in which each star contains a device called a hub. Figure 3-1 shows a USB bus topology. The USB enables connection of up to 127 devices via this tiered star topology. In addition, devices can be connected or disconnected while the system is still operating.

Figure 3-1. Bus Topology

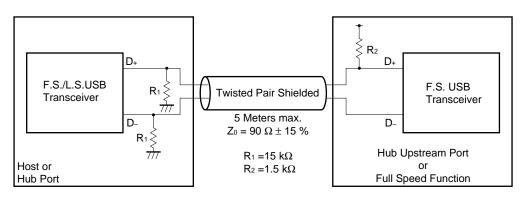

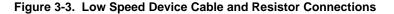

USB signals are transferred point-to-point as differential signals using two signal lines. There are two signal trace modes: full speed mode (12 Mbs) and low speed mode (1.5 Mbs). Low speed mode is used in low-cost devices such as mouse devices that do not require much EMI protection. As shown in Figures 3-2 and 3-3, the mode is set as full speed or low speed based on the position of the terminating resistors connected to both ends of the USB cable. Terminating resistors are also used at each port to detect when devices are being connected or disconnected.

Figure 3-2. Full Speed Device Cable and Resistor Connections

The host schedules and manages data transfers. Consequently, transfers must always be started by the host, and all transfers are performed using up to three packets (token, data, and handshake packets). The token packet sends USB devices information on the processing direction, type of transaction, address, endpoint, etc. The USB device decodes the address field and determines whether or not it has been accessed. The data packet contains the data that is sent in the direction (from host to device or from device to host) that is specified by the token packet. The handshake packet is returned to the source of the transfer to indicate whether or not the transfer was successful. The following four types of transfers occur between USB hosts and USB devices.

- Interrupt transfer

This is a small data transfer which is used to send information from a USB device to client software. The HCD (Host Controller Driver) sends a token packet to a device within the period required by the device, after which the USB data transfer is executed.

- Isochronous transfer This is a periodic data transfer that uses a constant data transfer rate.

- Control transfer

This is a non-periodic data transfer that is used to send information about configuration, commands, and status between the client software and a USB device.

- Bulk transfer

This is a non-periodic data transfer that is used to send large amounts of information

between the client software and a USB device.

Under OpenHCI, data transfers are divided into two categories: periodic and non-periodic. Periodic transfers, which are executed within a specified period, are further divided into the interrupt and isochronous transfer types. Non-periodic transfers, which are not executed periodically, are divided into control and bulk transfer types.

To implement the following types of operations, a device called a USB host controller and software called the USB HCD must both be installed on the host computer. OpenHCI is the specifications that apply to the relation between the host controller and the HCD software. This device complies with the **Open HCI Specification Release 1.0** and **OpenHCI Legacy Support Interface Specification Release Version 1.01**.

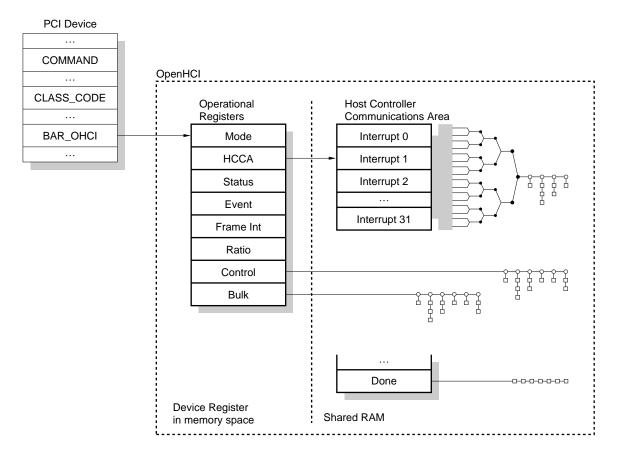

#### 3.2 Host Controller's Communication Method

The host controller (HC) and the host controller driver (HCD) communicate via the following two paths.

- Operational registers

- Host Controller Communications Area (HCCA)

In communication that uses the operational registers which are built into the HC, the HC is the PCI target device. The operational registers are a set of registers that include control bits, status bits, list pointers, etc. They also include pointers that indicate the position of the HCCA (Host Controller Communications Area) within system memory. The HC becomes the PCI bus master for communications that are executed via the HCCA. The HCCA is a 256-byte system memory area that contains head pointers to the interrupt ED list, head pointers to the Done Queue, and frame-related status information. The software uses this system memory to directly control the HC's functions without reading from the HC, as long as operation conditions are normal (i.e., there are no errors). These two paths are used for handling HC control tasks and USB data transfer results.

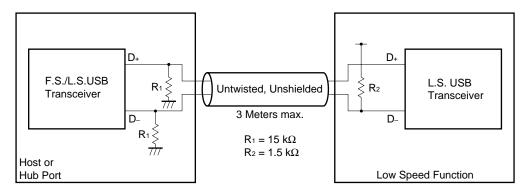

The HCD executes communication between the HC and USB devices, based on the enqueued ED (Endpoint Descriptor) and TD (Transfer Descriptor). An ED contains information (maximum packet size, endpoint address, endpoint speed and data flow direction) that the HC requires to communicate with the endpoint, and the ED can also be used as the TD queue's anchor. The HCD generates EDs and assigns them to the various endpoints, when are then listed and linked.

A TD contains information (data toggle information, buffer positions in system memory, and complete status code) that is required for the data packet to be sent. Each TD also contains information (data buffer size ranging from 0 to 8192 bytes, with a maximum of 1024-byte transfer per data packet) that is related to at least one data packet. Enqueued TDs are serviced in FIFO order. The TD queue is linked with a certain endpoint's ED and the TDs are linked with the TD queue. The HCD generates data from this structure and passes the data to the HC for processing.

Figure 3-4 shows the relation between EDs and TDs.

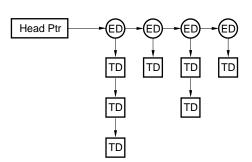

ED lists are categorized into four types: bulk, control, interrupt, and isochronous. Three types of head pointers of ED list are held (one for each of the above types except isochronous). The isochronous ED list is simply linked following the interrupt ED. The head pointers to the bulk and control ED lists are held in the operational registers, while the head pointers to the interrupt ED list are held in the HCCA. There are 32 interrupt head pointers, and the head pointer that is used by a frame is determined based on the usage of the frame counter's low-order 5 bits (indicating the addresses of the 32 types). The interrupt ED list structure is a tree structure, as is shown in Figure 3-5, in which the execution interval is determined according to the depth of the points where several paths intersect. In other words, interrupt EDs that are linked to the root of the tree structure are allocated and executed at a rate of 1 ms per ED.

#### Figure 3-5. Interrupt ED List

Figure 3-6 shows how the OpenHCI's bandwidth is allocated. The HC selects the list to be serviced based on a prioritization algorithm. Control and bulk lists take priority from the start of the frame to the point where HcFmRemaining becomes HcPeriodicStart.

When HcFmRemaining becomes HcPeriodicStart, periodic list servicing takes priority. The priority of periodic list servicing is higher than that of control or bulk servicing up until the point where periodic list servicing is completed or the frame period is completed. After periodic list servicing is completed, control or bulk list servicing is resumed.

Time

Interrupt/isochronous list servicing begins with servicing the interrupt ED head pointer that is serviced for the current frame. Since isochronous lists are attached after interrupt lists, interrupt lists must have a higher priority than isochronous lists. Bulk and control list servicing resumes at the point in each list where servicing was interrupted. When servicing reaches the end of the list, a value is loaded from the head pointer and servicing continues. The control endpoint is given access privileges that are at least equivalent to those of the bulk endpoint, and this service ratio is determined by ControlBulkServiceRatio in HcControl. Figure 3-7 shows an example where the control/bulk service ratio is 4:1. When control and bulk take priority, the HC executes ED servicing of each list according to the ControlBulkServiceRatio.

Figure 3-7. When Control/Bulk Service Ratio Is 4:1

This control/bulk service ratio is retained over several frames. As soon as the HC services the data packet for one of the TDs included in an ED, it begins servicing the next ED.

#### 3.3 Endpoint Descriptor

An ED is always allocated in 16-byte units to system memory. When the ED list is referenced, if it contains a TD that is linked to an ED, the HC executes the transfer specified by that TD. If the HCD must change the head pointer (HeadP) value, list servicing for all EDs that have the same transfer type as the ED to be deleted must be rendered invalid so as to prevent the HC from accessing the EDs. Therefore, the HCD sets a Skip bit.

#### 3.3.1 Endpoint descriptor format

#### Figure 3-8. Endpoint Descriptor Format

| ;                                 | 2   | 1               | 1 | 1                                                     | 1                                                                   | 1 1                                                                                                                                                                                                                                                       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----------------------------------|-----|-----------------|---|-------------------------------------------------------|---------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|